## Comp 182 Chapter 3 Digital Logic Level

### Gates

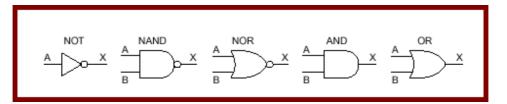

And, Or, Not

Nand, Nor

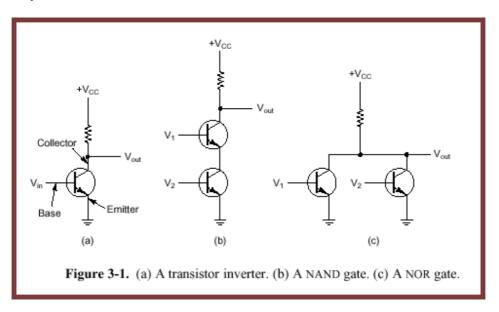

### How they are created.

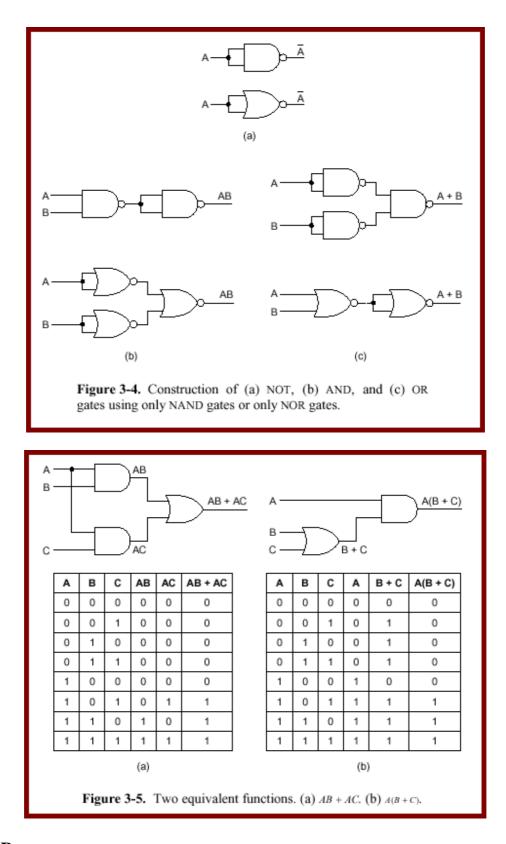

The inverter is a Not. Typically the Not, Nand, Nor gates are used as the basic building blocks because they can be created with fewer transistors.

If an and gate is required - for example - it can be created by tying a a Nand to a Not.

### **Boolian Algebra - Nomenclature.**

If we designate A and B as inputs to a gate, and X as the output we write:

AB = X for A And B = X

$$A+B = X$$

for  $A \ Or B = X$

$\overline{AB} = X$  for  $Not (AB) = X$

Symbols

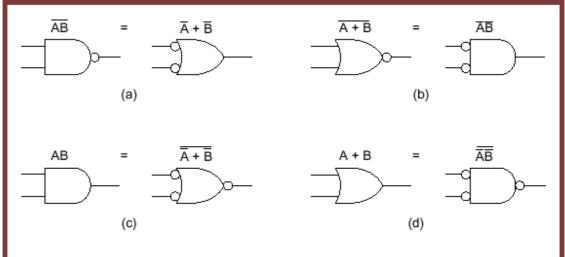

### **Truth Tables**

### Identities

These are the rules of boolian algebra - similar to the rules of normal algebra. Eg. in normal algebra A x B = B x A, but A - B  $\Box B$  - A.

| Name                                            | AND form                                      | OR form                                       |

|-------------------------------------------------|-----------------------------------------------|-----------------------------------------------|

| Identity law                                    | 1A = A                                        | 0 + A = A                                     |

| Null law                                        | 0A = 0                                        | 1 + A = 1                                     |

| Idempotent law                                  | AA = A                                        | A + A = A                                     |

| Inverse law                                     | $A\overline{A} = 0$                           | A + Ā = 1                                     |

| Commutative law                                 | AB = BA                                       | A + B = B + A                                 |

| Associative law                                 | (AB)C = A(BC)                                 | (A + B) + C = A + (B + C)                     |

| Distributive law                                | A + BC = (A + B)(A + C)                       | A(B + C) = AB + AC                            |

| Absorption law                                  | A(A + B) = A                                  | A + AB = A                                    |

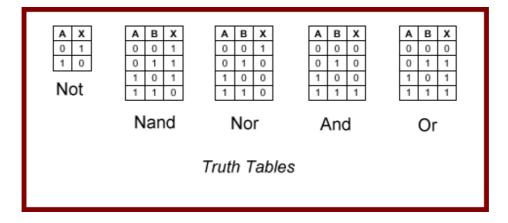

| De Morgan's law                                 | $\overline{AB} = \overline{A} + \overline{B}$ | $\overline{A + B} = \overline{A}\overline{B}$ |

| Figure 3-6. Some identities of Boolean algebra. |                                               |                                               |

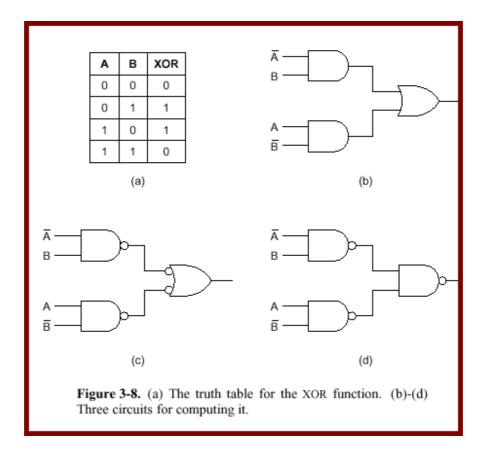

Given these identities, with a bit of thought it can be seen that there is more than one way to accomplish the same truth-table.

Figure 3-7. Alternative symbols for some gates: (a) NAND. (b) NOR. (c) AND. (d) OR.

XOR

### **Basic Digital Logic Circuits**

### **Combinational Circuits**

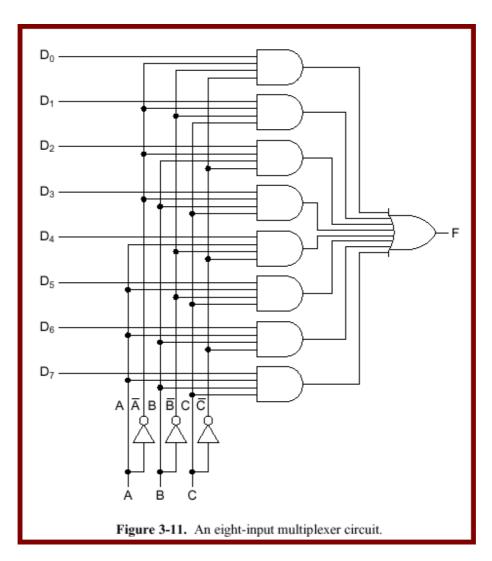

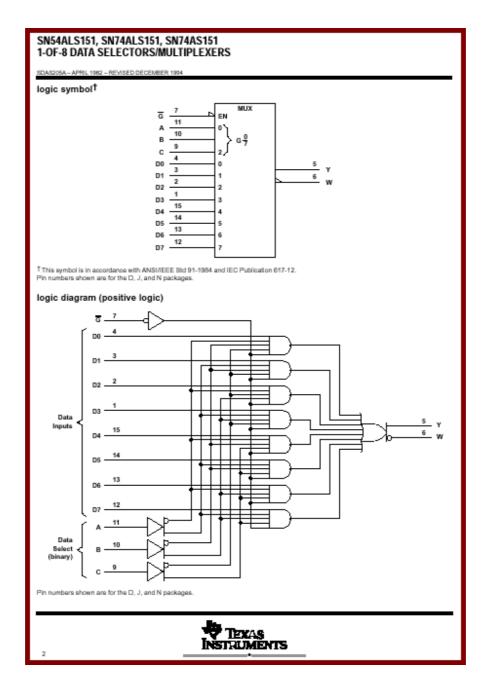

• Multiplexers - Selects one of n inputs.

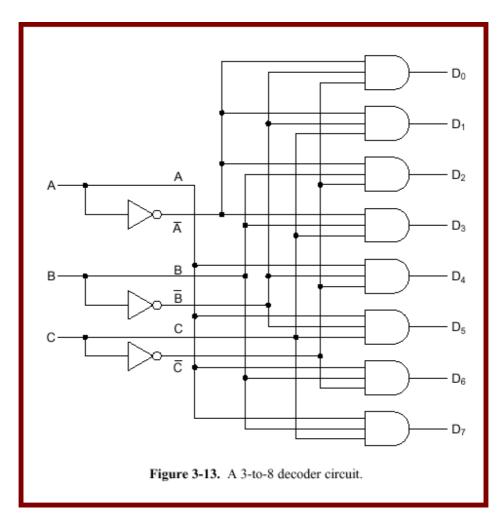

• Decoders - Sets one of n outputs.

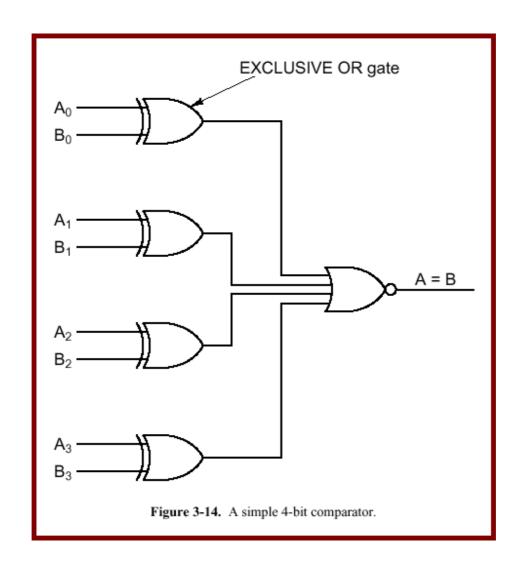

• Comparators - Are the inputs the same?

### Arithmetic circuits

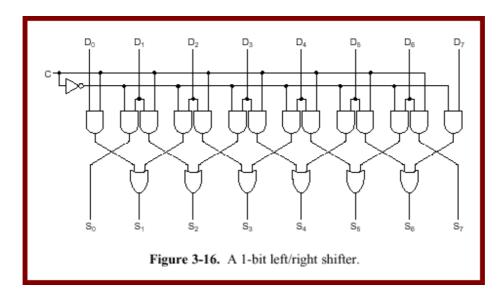

• Shifters - Move a bit left or right (multiply/divide by 2).

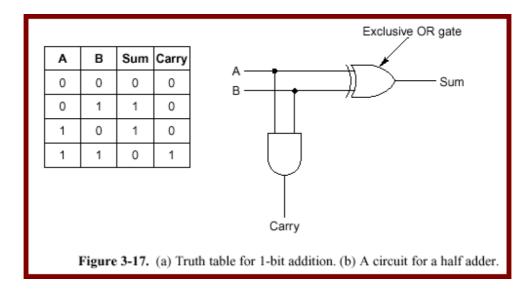

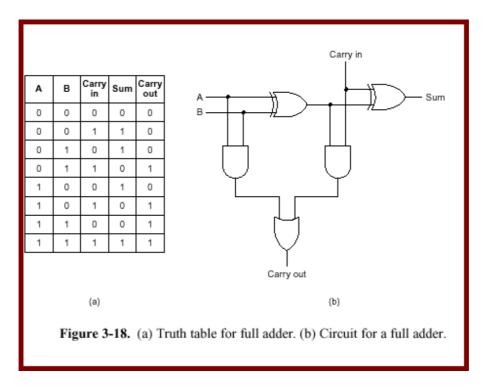

• Adders - Add the bits together.

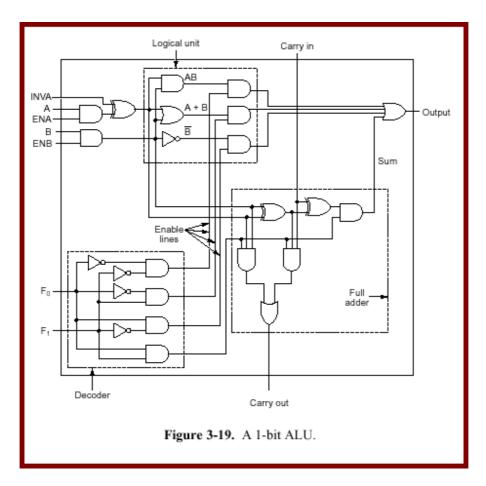

• ALU's

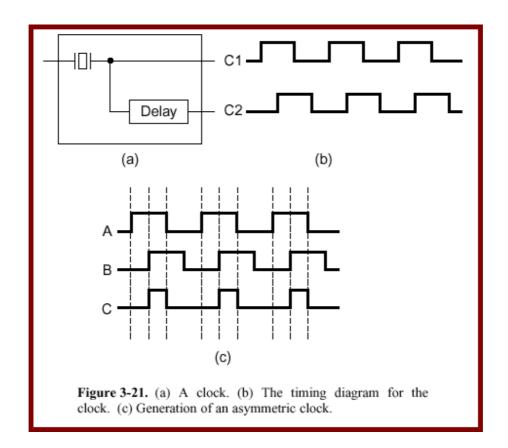

• Clocks - When to do it.

### Memory

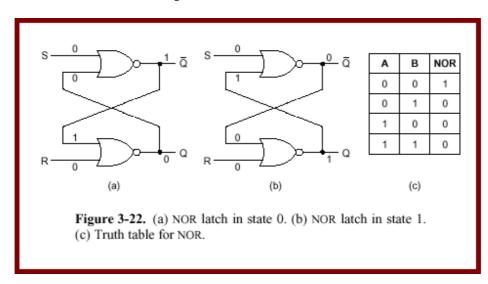

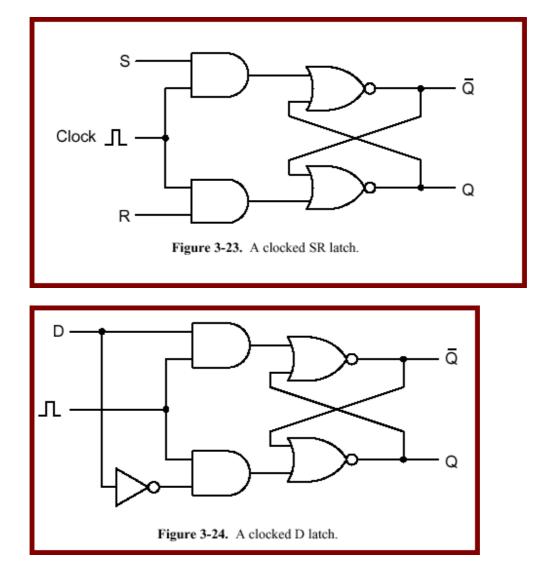

• Latches - switched on input value

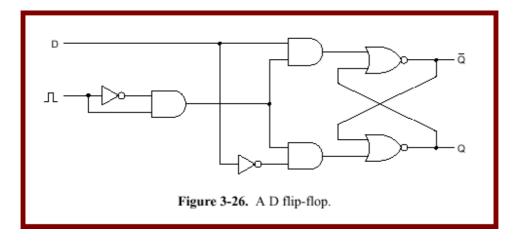

• Clocked Latches set to input value when clocked

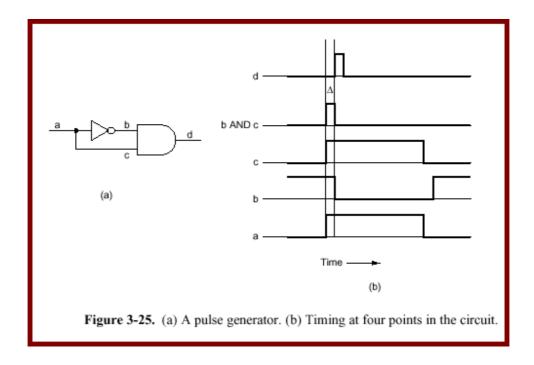

• Rising/falling pulse

• Flip-Flops set on rising or falling pulse

• Registers

Memory Organization

RAM, ROM

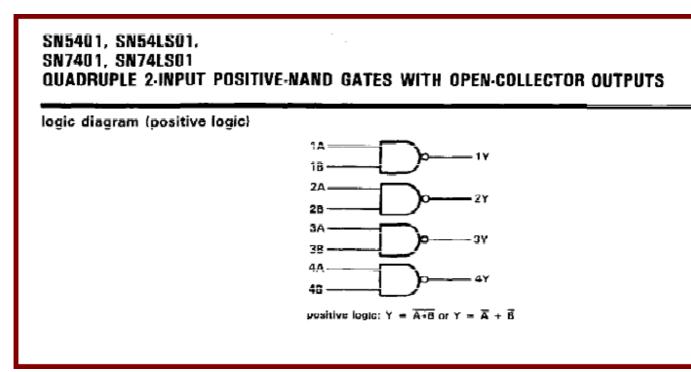

# **Integrated circuits - Some Real** *Texas Instruments* **Products**

4 Nand gates

<u>Multiplexer</u>

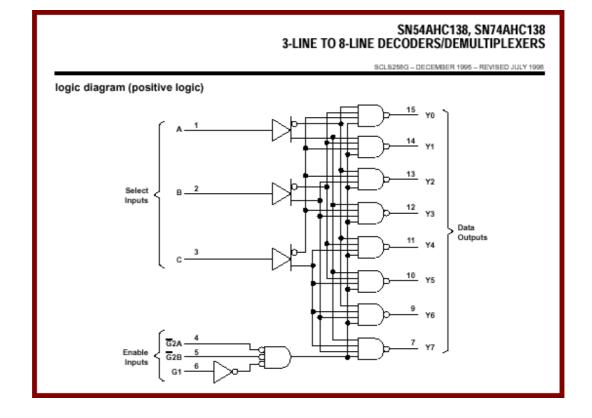

<u>Decoder</u>

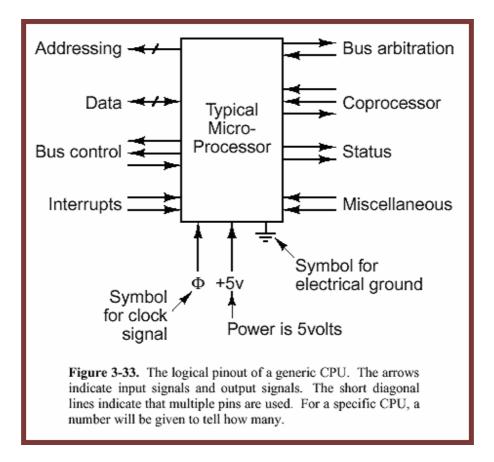

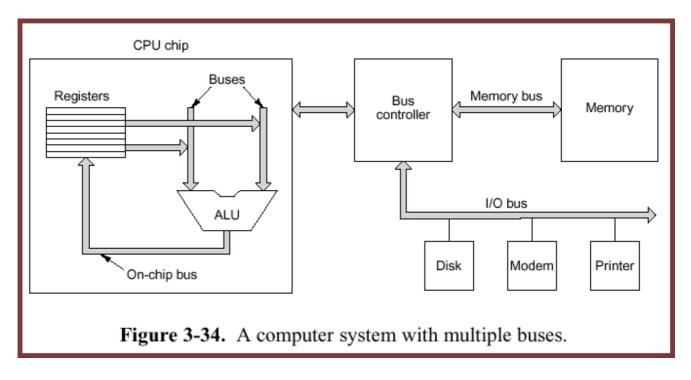

### CPU Chips

Buses

Width

Clocking - speed

Syncronous

Asyncronous

Arbitration

Interrupts

Example CPU Chips

- Pentium II

- UltraSPARC II

- picoJava II

Example Buses

ISA

PCI

USB

Interfacing

I/O Chips

PIO - 8255

Address Decoding